You can’t fix what you don’t see

The board-agnostic FPGA visibility layer

for verification.

More than 100,000 x JTAG at speed, on any board.

You go to production in 12 weeks. Your simulation says the design is clean. Your FPGA prototype says it isn’t — JTAG can only see 30 milliseconds.

Exostiv captures hours, at-speed, on any board.Find the bug this afternoon, not next sprint.

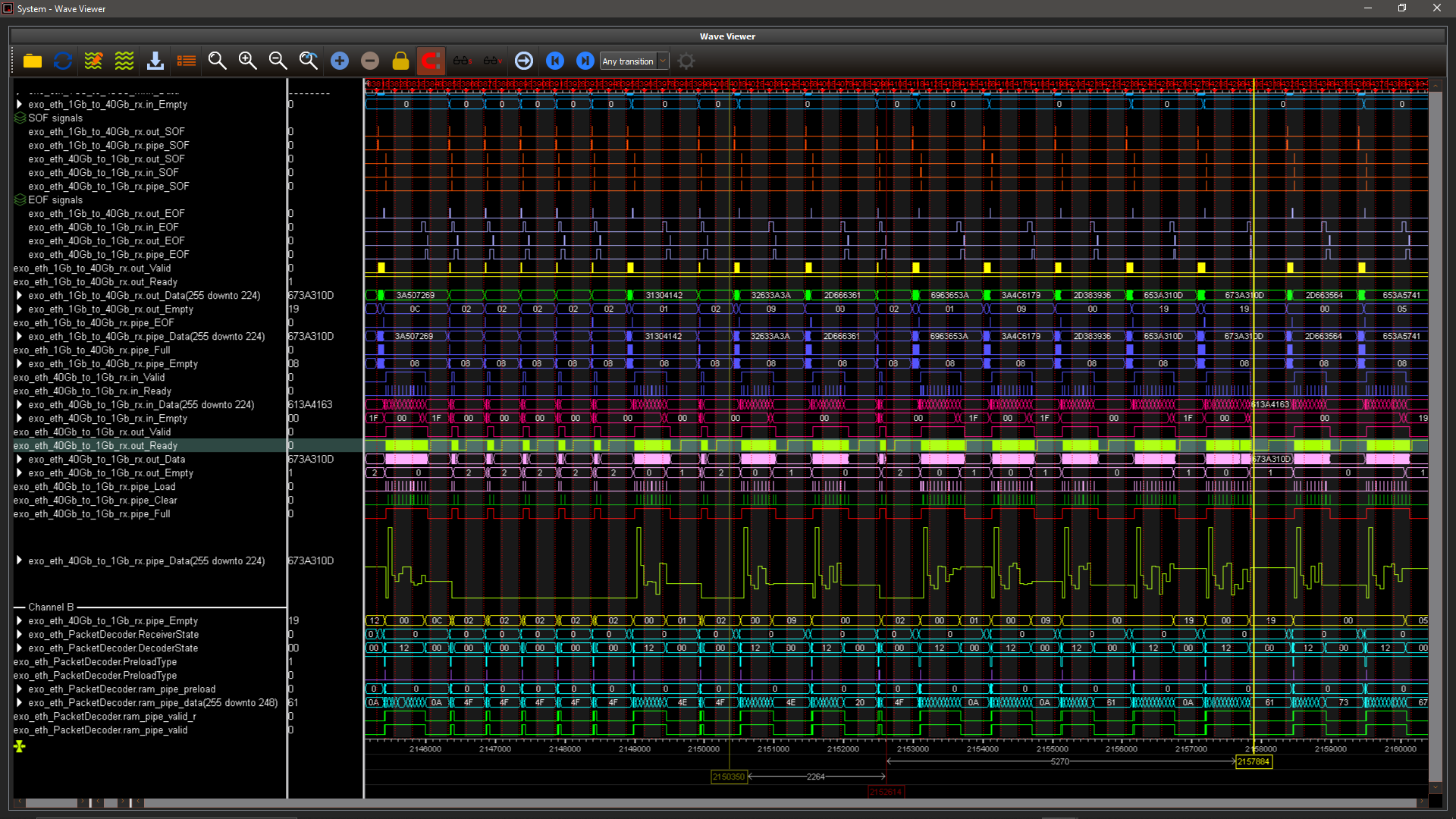

A one hour capture from FPGA in 45 seconds

A capture from a 60 fps video interface (148 MHz). We trigger on 232,000 frames,

capturing the start of each successive video frame during more than 1 hour.

The total capture is 8GB, sampled from a live FPGA – finally displayed in the waveform viewer

How does it work?

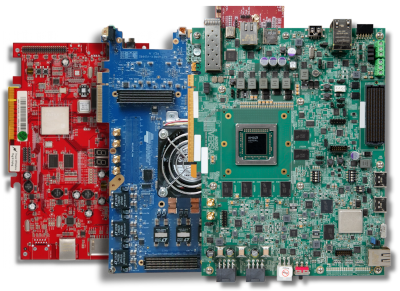

Exostiv Labs tools add a ‘no-JTAG’ board-agnostic visibility layer to FPGA-based systems used for verification.

It leverages FPGA logic and transceiver resources with powerful external hardware to massively capture data and view your system behaviour from inside at speed of operation.

Exostiv Labs solutions…

- scale with the target platform complexity

- are FPGA plaftorm-independent

- operate at speed over realistic nr of cyles